COMPUTER SERVICE MANUAL

# Special thanks to plool tokensonly.com 2010

Distributed by: William Arkush

VIDEO GAME DATA IBRARY

2876 Culver Ave. Dayton, Ohio 45429

**VOLUME II**

(513) 296-9330

(C) COPYRIGHT 1975

#### TABLE OF CONTENTS

| TITLE                            |      | S | CHI | EM/ | TIC | SE | CT | Ю | N P | 10 |  |   |    | P  | AGES |

|----------------------------------|------|---|-----|-----|-----|----|----|---|-----|----|--|---|----|----|------|

| GENERAL INFORMATION              | n. 9 |   |     |     |     |    |    | ٠ |     |    |  | ٠ |    |    | 1,2  |

| ROM INFORMATION                  |      |   |     |     |     |    |    |   |     |    |  |   |    |    | . 4  |

| POWER SUPPLY                     |      |   |     |     |     |    |    | ٠ |     |    |  |   |    |    | . 5  |

| TIMING, SYNC & VIDEO SUMMATION . |      |   |     |     | . 1 |    |    |   |     |    |  |   |    |    | 6,7  |

| R CAR GENERATION & CONTROL       |      |   |     |     | . 2 |    |    |   |     |    |  |   |    | 7  | ,8,9 |

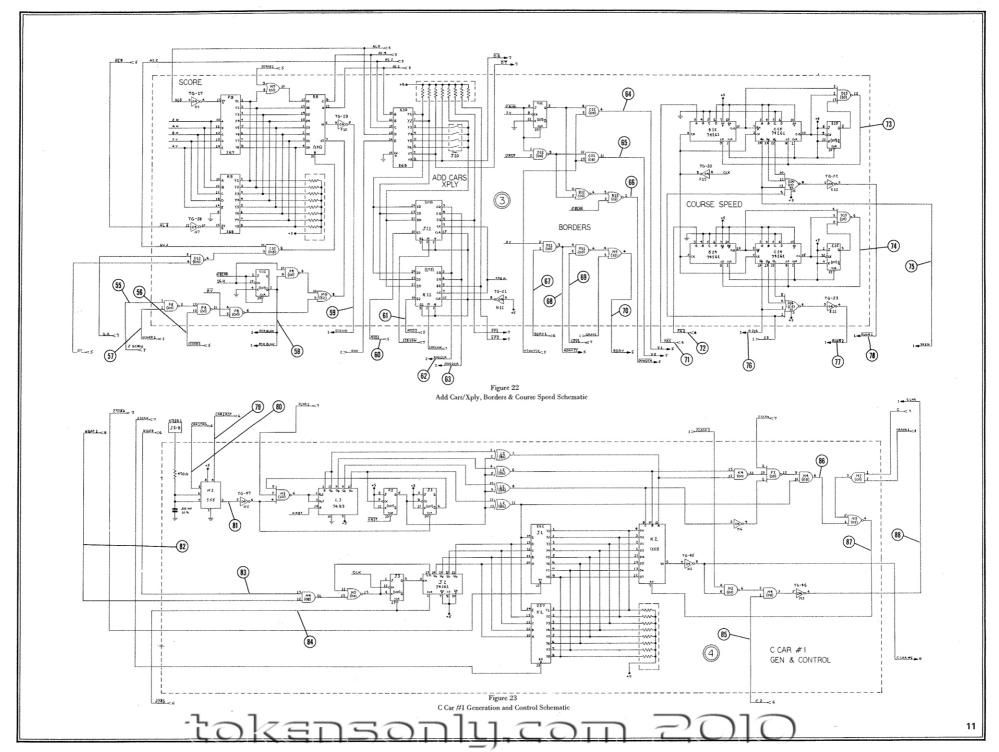

| SCORE, ADD CARS & COURSE SPEED . |      |   |     |     | . 3 |    |    |   |     |    |  |   | 9  | ,1 | 0,11 |

| C CAR #1 GENERATION AND CONTROL. |      |   |     |     | . 4 |    |    |   |     |    |  |   |    | 1  | 1,12 |

| THE PROCESSOR                    |      |   |     |     | . 5 |    |    |   |     |    |  |   | 12 | .1 | 3,14 |

| C CAR #2 GENERATION & CONTROL    |      |   |     |     |     |    |    |   |     |    |  |   |    |    |      |

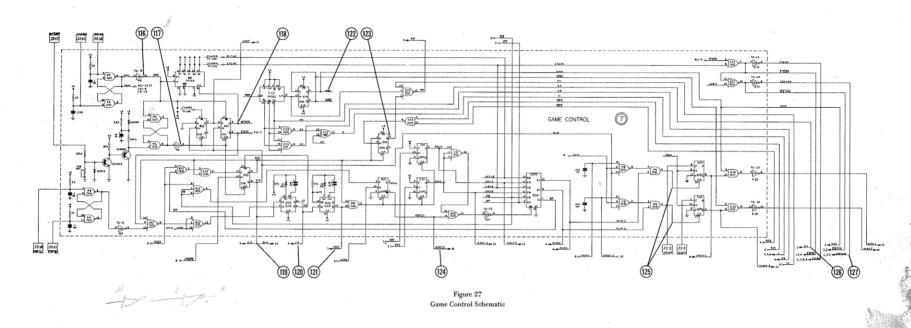

| GAME CONTROL                     |      |   |     |     | . 7 |    |    |   |     |    |  |   | ٠. | 1  | 5,16 |

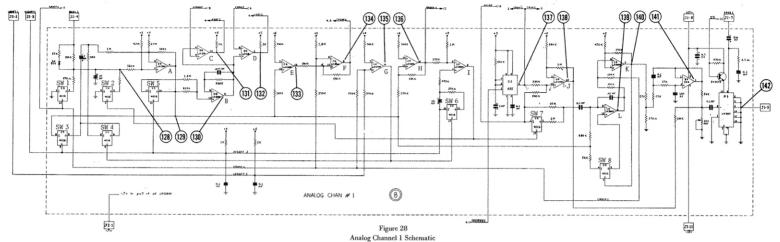

| ANALOG CHANNEL #1                |      |   |     |     |     |    |    |   |     |    |  |   |    |    |      |

| ANALOG TIMING                    |      |   |     |     |     |    |    |   |     |    |  |   |    |    |      |

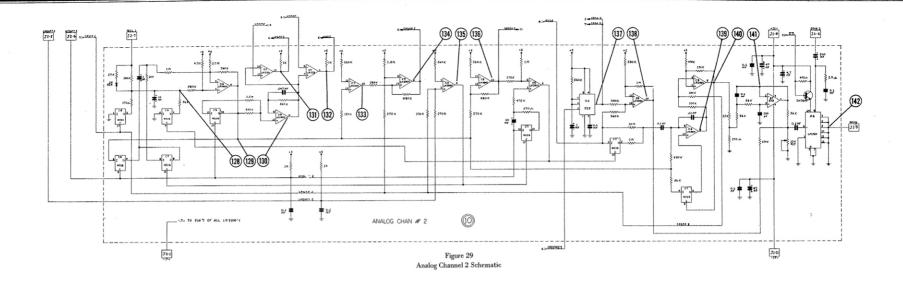

| ANALOG CHANNEL #2                |      |   |     |     |     |    |    |   |     |    |  |   |    |    |      |

| LAMP DRIVERS                     |      |   |     |     |     |    |    |   |     |    |  |   |    |    |      |

# LOGIC SYMBOLOGY & NOTATION

The function and operation of logic circuits is described using standard logic symbology and notation. All logic functions are also described using the positive logic convention. Positive logic is a system of notation where the more positive of two levels is called the HI or (1) state and the more negative is known as the LO or (0) state. All logic circuits are of the TTL family or are directly TTL compatible. The specific voltages are +2.4 volts to +5 volts for logic HI and 0 to +0.8 volts for logic LO. Signal names overscored (e.g. V RST and pronounced "vertical rest not") go Lo to initiate events (active LO) and those not overscored go HI when active. Overscored signals are always at the logic level opposite their non-overscored counterparts.

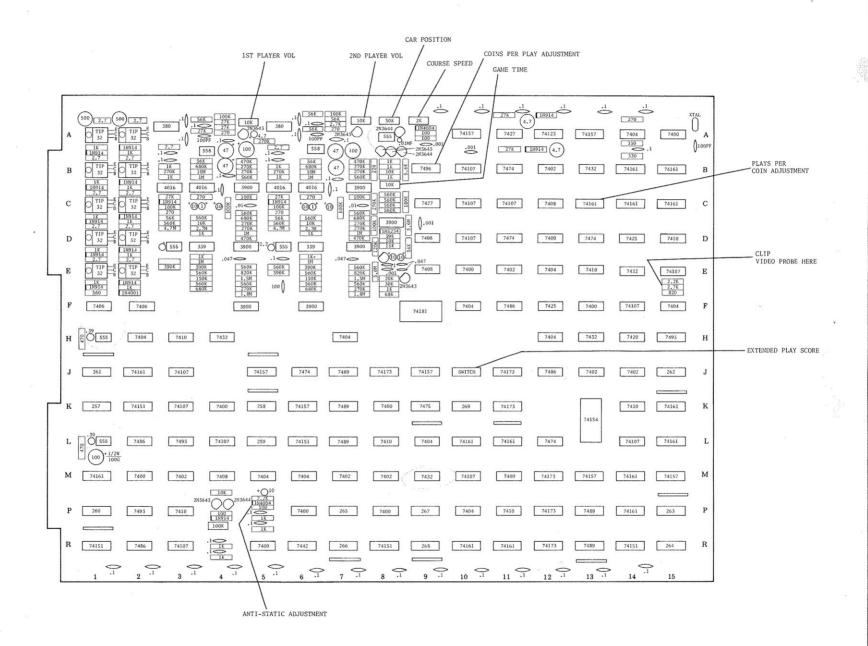

Logic pacakges are identified in the text and in the logic schematics by their actual grid locations on the printed circuit board (PCB). For example, chip A3 is located at the intersection of the A column and the third row. Pins are identified by a third number. For instance, A3-1 refers to the first pin to the left of the reference notch of the IC.

Discrete components are not as easy to locate for they are not positioned in a way as to be readily identifiable by PCB grid coordinates. Some discretes are easy to locate because of prominent features; others will require laborious following of the appropriate PCB traces. The more important discrete components are identified in the illustration of the printed circuit board computer (page 4).

## THE TEST POSITION

When mounted in the cabinet, the monitor of this game is rotated  $90^\circ$  to take advantage of the width of the CRT. Since this is not the normal position of a monitor, we will assume the monitor is rotated back  $90^\circ$  to its normal or "test" position for the discussion and test points in the following text. In other words, the cars are pointed to the left of the CRT, not to the top.

#### **PCB ADJUSTMENTS**

A number of circuits are adjusted by devices on the printed circuit board. Most of these adjustments are accomplished by turning trim pots, however the extended play score is adjusted by sub-miniature slides switches and two coin circuit adjustments can be made by moving the positions of jumper wires. The positions of all PCB adjustments are indicated on page 4. The terms "clockwise" and "counter-clockwise" refer to those directions when facing the slotted thumbwheel of the trim pot.

IST PLAYER VOLUME: To increase Channel 1 volume, turn this pot clockwise. 2ND PLAYER VOLUME: To increase Channel 2 volume, turn this pot clockwise. CCAR POSITION: Adjust this pot so the controlled car(s) are centered in the desired area of the CRT.

GAME TIME CONTROL: Since this adjustment affects the course speed, the game length must be adjusted prior to course speed adjustment. Clockwise rotation increases game length and the recommended time is 90 seconds. COURSE SPEED CONTROL: Clockwise rotation increases the course speed and, generally speaking, the speed should be adjusted so a good player with only two crashes can barely reach the extended play score.

ANTI-STATIC ADJUSTMENT: Turn this pot counter-clockwise all the way and then start a new game. Rotate clockwise until the game shuts off, then back off a bit. Test adjustment according to instructions in the Game Control analysis.

EXTENDED PLÁY SCORE: This adjustment is made by changing the positions of the sub-miniature switches located at J10. Initial setting should provide extended play at a score of 400.

COINS PER PLAY: Since this adjustment is pre-set by the factory at one

coin per single player game and two coins per two player game, it will normally not need adjustment. However, if adjustment is necessary to accommodate a foreign currency structure, see the Game Control analysis. PLAYS PER COIN: Changing the position of the jumper wire to B11-4 will change the game from one to two plays per coin in the single player mode and from one to two plays per two coins in the two player mode.

#### TEST EQUIPMENT

The test data found in the text are referenced to three test instruments which you must have in order to fully troubleshoot this computer: the logic probe, the yideo probe and the oscilloscope.

LOGIC PROBE: The logic probe is a digital test instrument designed for checking integrated circuit outputs. The probe indicates if the examined signal is a logic HI, LO or changing states (PULSING). All logic probe test point data are referenced to the Kurz-Kasch Model LP-520, however a number of other manufacturers such as Tektronix, Hewlett-Packard, etc. offer comparable logic probes.

THE VIDEO PROBE: the video probe is a simple, but extremely useful, test device. It consists of two IC test clips (or one clip and a test prod), a length of rubber-coated wire and a  $4.7 \mathrm{k}$ , 1/4 Watt carbon resistor. To use the video probe, connect the clip to the negative side (-) of the video coupling capacitor (page 4) and touch the probe tip to the node under examination.

The video probe simply couples the desired signal directly to the TV monitor where it is displayed on the CRT along with any other information already entering the monitor through the video input line. The video probe is useful for viewing signals used in the development of other signals where the developmental signals are not otherwise visible. Generally, a number of signals are used in the development of a final video display and the video probe provides a graphic display of the development process. Unfortunately, the video probe can only be used for viewing video signals. Extremely fast signals such as CLK will not be displayed and nor will it display either analog or very slow digital signals.

If desired, a separate video monitor may be used to display video probe signals, however frame sync will need to be connected to this monitor as well. Also, there is no real limit to the number of signals which can be displayed at any given time, however each new signal requires clipping on another probe or jumper wire. If a number of probes are connected in this way, a composite of developmental signals can be displayed to check the processing of complex video displays.

OSCILLOSCOPE: Although most computer malfunctions can be successfully tracked down using only a logic probe and a video probe, the use of an oscilloscope is highly recommended as there are a great many timing relationships in this game which cannot otherwise be examined. Additionally, the only way analog waveforms can be accurately examined is with an oscilloscope.

## **TEST DATA**

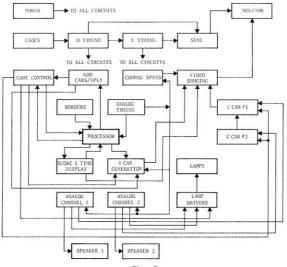

To check test points, first consult the block diagram (Figure 7) to locate the suspected and related circuits. The test points are arranged in a logical order beginning with developmental signals and ending with section outputs. First, check the section outputs and, if correct, you are in the wrong area entirely. If not OK, proceed to check developmental signals. Follow these signals backwards until you find correct inputs or signals. The malfunction must then be in that area between the correct inputs and incorrect outputs, if all the signals in a section appear incorrect, examine related section outputs using the block diagram as a general guide.

Data for a signal or test point is given only for those instruments which are capable of testing that signal. Since the logic probe is incapable of checking analog signals, logic probe test data will appear only for digital signals. And, although some indication of signal periodicity is obtainable from the logic probe, oscilloscope data will take precedence where precise timing relationships or specific signal periodicity are in question.

Likewise, video probe data will be given only for those digital signals which are capable of being displayed by the monitor and they are presented in two forms: (1) Verbal explanations are used where the appearance of the signal is readily described in words and not too complicated in form. Please bear in mind that the signal you see displayed on your CRT may not exactly correspond to the description you read in the text due to the fact that these descriptions are, of necessity, highly condensed. Minor discrepancies should not be a cause for concern since, generally

speaking, malfunctioning signals will show marked distortion. (2) Actual illustrations may be used for complicated or especially important signals where verbalization would be inadequate. This type of information is indicated by a reference to a specific figure number.

Oscilloscope data for digital signals includes only the duration and frequency of the pulse in question. Analog signals are generally described by a characterization of the waveform. Where precise timing relationships or unusual waveforms are difficult to describe, illustrations or oscilloscope photographs will be included.

The test instrument names are abbreviated in the test point data descriptions, where LP = Logic Probe, VP = Video Probe and SC = Oscillocscope.

## **RASTER SCAN NOMENCLATURE**

A number of terms associated with the control of the electron beam are explained here in preparation for a later section dealing with the generation of the sync signals. Since these signals are timed with the movements of the electron beam, the resulting relationships are quite important,

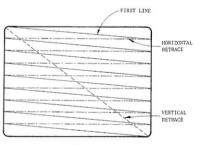

The TV monitor controls the vertical and horizontal deflection of the electron beam so it creates an endlessly repeated pattern of lines known as the raster. Figure 1 is a simplified illustration of the non-interlaced raster scan used in this game. The electron beam theoretically begins the frame in the upper left corner of the CRT and is deflected so it sweeps one horizontal line ending at the right. The beam is then repositioned back to the left side by a process known as horizontal retrace. During retrace, the video information is blanked out so no undesired illumination can occur. Retrace blanking is an internal function of the monitor and is not related in any way to any "blanking" signals produced by the computer, except that both occur more or less simultaneously. Computer signals V BLMK and H BLMK are used in the development of sync as well as in other circuits.

Figure 1 Raster Scan Nomenclature

After the electron beam has been reset to the left again, it sweeps the second horizontal line. Since the beam is deflected vertically as well as horizontally, the second line appears beneath the first. The beam continues to scan in this fashion until the end of the last line which is located in the lower right corner of the CRT. At this point, the beam is reset back to the left and to the top to the place of its beginning. This reset process is known as vertical reset and the video information is blanked out during this time.

Each time the electron beam has scanned the entire CRT, it is said to have completed one full field which contains 272 horizontal lines. In the non-interlaced raster scheme, successive fields are laid approximately on top of one another. Two complete fields constitue one full frame and the monitor frame rate is 30/sec.

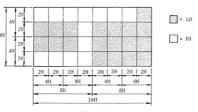

# **DEFINING CRT LOCATIONS**

Confusion has frequently arisen about some of the terms used to describe computer events and video probe displays with respect to CRT locations. For example, 128V is said to be LO in the upper half of the CRT which may appear to be confusing unless you understand that signal 128V is LO for the first 128 horizontal lines (or counts of the vertical sync chain), rises HI for another 128 counts, etc. When viewed with the video probe, 128V causes the upper half of the CRT to darken.

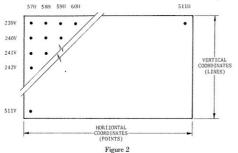

The combination of the vertical and horizontal addresses produces a set of coordinates for every point in the raster. For example, to illuminate a point in the approximate center of the CRT, the electron beam must be intensified as it reaches the intersection of 367V and 284H.

The nomenclature associated with this system is illustrated in the figure above. In most cases, the first line is denoted IV (1st Vertical). However, due to the unique construction of the sync circuitry in this game, the first line is numbered 239V. Since the raster contains 272 lines, the last line occurs at 511V. Every addressable point along each of these lines also has a location or number. In this game, the first point occurs at 57H, the second at 58H and so on until the end of the line which occurs at 51H.

The Coordinate System

## THE WINDOW PARADOX

The term "window" is one which has been coined to describe the area of the CRT affected by the condition or state of the signal. A certain paradox exists when using this term because vertical signals produce horizontally appearing windows and visa versa. For example, the horizontal signal 128H appears as a set of alternating light and dark vertical columns or windows. Since the electron beam is intensified whenever the input is HI, it will cause the first 128 clock pulses (two clock pulses equals IH) to be dark, the next 128 light and so on (Figure 3). Each line is scanned the same way as long as the signal is present, so the result will appear as a set of vertical windows when all 272 lines are stacked on top of each other. The dark areas are called LO windows and the light ones HI windows.

Figure 7 The Block Diagram

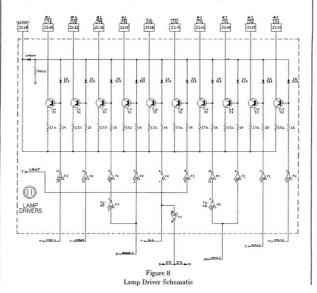

## THE LAMP DRIVER CIRCUIT

Power for this circuit (+15 volts peak-to-peak) is supplied through pin 19 of J1 and is connected to the emitters of all the driver transistors through 270G resistors. Each transistor also has a 1N914 diode wired across the +15 volt line and the base of the transistor which provides one diode drop. This causes the potential at the base to be 0.6 volts lower than at the emitter to insure the transistor is adequately turned on when the output of the associated inverter goes LO. When the appropriate input signal goes HI, the inverter output drops LO, forward biasing the transistor and turning on the associated lamp.

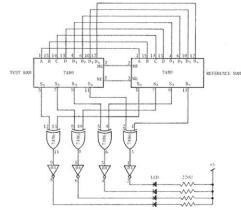

# THE ROM READER

Thirteen separate 256-bit ROMs (Read Only Memories) are used in Wheels II to store image information and to generate miscellaneous signals. ROMs are not complex devices, but they can be a headache to troubleshoot. Normally, correct ROM operation is most easily verified by the "substitution technique" where the technician simply plugs in a known-to-be-good ROM and if the game suddenly begins to function correctly, the other ROM must have failed. However, there are thirteen ROMs in this game and the technician must have the full set to have the substitution capability. Since each ROM is custom programmed and fairly expensive, this technique is unrealistic.

In order to test a ROM without using the substitution technique, the information must be read out and examined for correct logic levels. This can be done with a logic probe by tying the address inputs at the desired word and checking all eight bits for correct logic levels, but this is an extremely laborious process. Furthermore, you still need to know what the bit pattern in a good ROM should be.

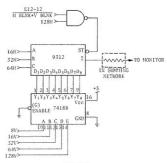

The following procedure eliminates the cost of the substitution technique and the labor of the logic probe by displaying the entire bit pattern of the RCM on the monitor CRT. However, the procedure does require assembling a small "test station", but this should take only a few minutes. The only parts required are three IC sockets (two 16 pin and one 14 pin), a 2" by 4" piece of vector board, a 9312 8-to-1 multiplexer, a NAND gate and a few feet of #30 ANG wire.

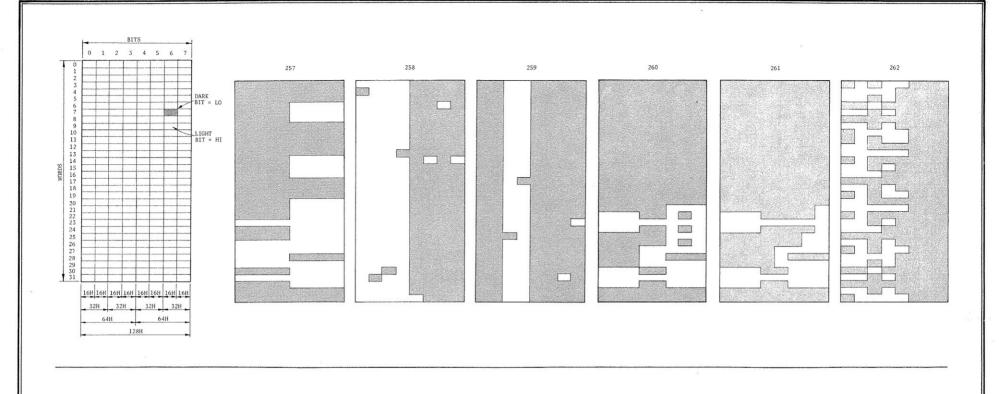

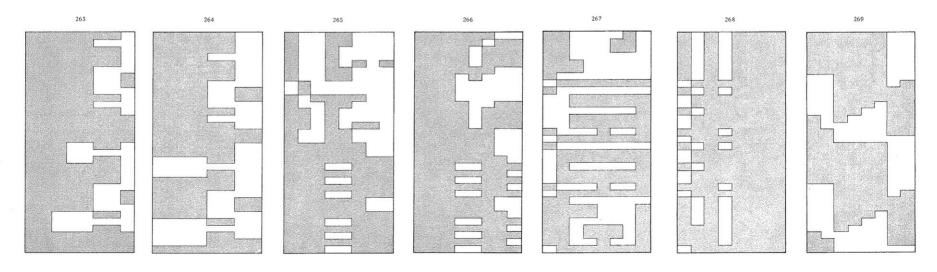

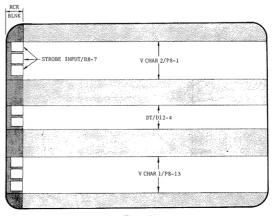

Connect the IC sockets as indicated in Figure 9. Power, ground and all signal inputs are readily found on your Wheels II PCB. Insert the multiplexer and NAND gate and the ROM is question. The result will be a bit pattern displayed in the area of the CRT determined by the strobe input of the multiplexer (Figure 4). Simply compare the pattern you see on your monitor with the one in this manual under the appropriate ROM number.

Figure 9 ROM Reader Schematic

Before we discuss exactly what is happening in the test circuit, we need to make a few relevant comments about the RONs themselves. The 74188 is a fusable-link, 256-bit programmable read only memory (PROM) organized as 32 words of eight bits each. Each word is read out be a different five-bit address which causes all eight bits of that word to appear simultaneously at the Y1 to Y8 outputs.

The data can be electrically programmed at any of the 256 bit locations. Prior to programming, the memory contains LOs at all locations. The programming procedure simply blows fusable metal links which results in HI logic level conditions at the selected locations. The procedure is irreversable and, once programmed, the output for that bit is permanently programmed HI. Since the 74188 PROM is directly replaceable with the 74488 mask-programmed ROM; do not be alarmed if games in the future contains the less expensive mask-programmed device.

When plugged into the test circuit illustrated in Figure 9, the ROM data is organized into a rectangle which contains eight bits across the top 32 words down the CRT. The data is read out by a simple sync progression and directed to appear within the rectangle by the multiplexer. Since the multiplexer is strobed by 128H, the information is enabled only when 128H is LO which occurs in a wide vertical band in the center of the CRT (Figure 4). Also, notice that we have connected the signal from E12-12 to the strobe as well, which prevents sync disruption. The windows for the individual bits are developed by the code at the A, B and C selects which divides the 128H wide window into eight smaller 16H wide bit-windows.

THE PRINTED CIRCUIT BOARD COMPUTER

tokensonly.com 2010

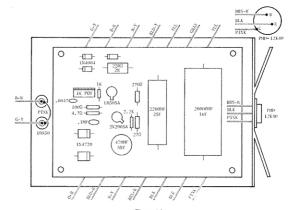

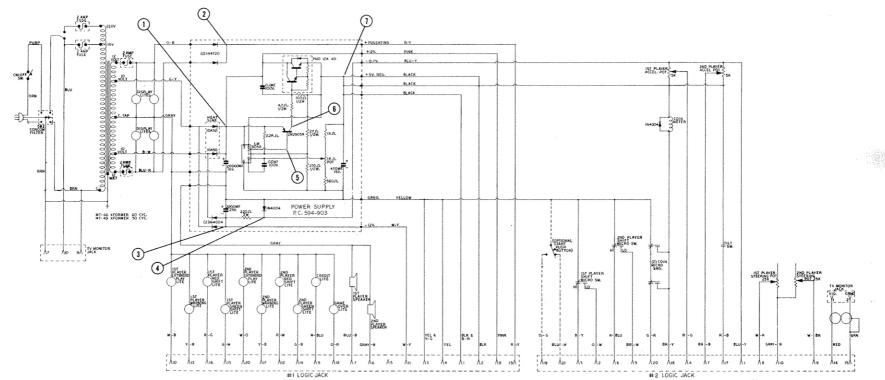

# THE POWER SUPPLY

The Power Supply consists of a transformer and a separate power supply PPCB containing four distinct sections which output a number of different voltages, both regulated and unregulated. The +12, -12 and -0.7 volt supplies are used in the analog circuitry and the +5 volt line powers the interrated circuits.

The line voltage is initially filtered by a Corcom line filter, which removes undesired transients before the transformer primary. The transformer has two secondary windings which produce 10 and 12 volts AC and these voltages are sent to the following circuits for processing:

(1) +15 VOLTS: The 12 VAC line is full-wave rectified by two 1N4720 diodes and the resulting unfiltered, unregulated pulsating waveform (about 15 volts peak-to-peak) is sent directly to the lamp driver circuit via pin 19 of logic jack J1.

(2) -12 VOLTS: The 10 VAC waveform from the other secondary is full-wave rectified by two 1N4004 diodes and the resulting voltage is negative with respect to ground because the cathodes of the diodes are wired to the transformer secondary. This pulsating waveform is filtered by a 2200 MF capacitor resulting in a filtered, but unregulated, -12 volt supply which is available to the analog circuitry through pin 11 of J1.

(3) 0.7 VOLTS: A diode wired across the -12 volt line and ground provides the potential of one diode drop (0.7 volts) which is used to offset the player's accelerator pots from ground and is also available to the analog circuitry through pin 1 of jack J2.

$(4) + 5 \, \rm VOLTS:$  This is a solidly designed, closely-regulated, high current supply which is fully adjustable by a 1k trim pot located on the Power Supply PCB. Initially, the 10 volt AC output from the transformer is full-wave rectified by two 10 amp, 50 volt (10ASO) diodes. This current is connected to a Darlington pass transistor (PMD12K4O) which is controlled by a 2N290S transistor operated by a LM30S integrated voltage regulator. This configuration is a standard current-limited, foldback supply where the amount of load controls the LM30S. The load is sensed by a voltage divider network consisting of a 2700 and a 27 $\Omega$  resistor which causes the LM30S to supply more or less base current to the Darlington pass transistor. As the base current to the Darlington rises, it supplies more output current, thereby stabilizing the voltage with respect to the load.

The voltage adjustment pot controls the LM305 feedback input and is connected between a voltage divider network wired across +5 volts and ground. As the potential at the pot increases, the 2N2905 is turned on harder, turning on the pass transistor harder which then supplies more voltage.

NOTE: The following test point measurements are made with a 20,000  $\!\Omega/V$  Volt-Ohmmeter at the indicated points.

1. +15 VDC 2. +12 VDC 3. ~15 VDC 4. -.7 VDC 5. +15 VDC 6. -6 VDC 7. +5 VDC

THIS CIRCUIT IS ADJUSTED WITH A VOM SO THE +5 OUTPUT IS EXACTLY 5.1 VOLTS

Figure 10 The Power Supply PCB

5

Figure 11

The Power Supply Schematic

#### THE OSCILLATOR

The Oscillator produces CLOCK, the master timing signal which synchronizes the entire computer. The crystal generates a 14.318 MHz frequency and is kept oscillating by two closed-loop amplifiers which consist of a feedback resistor and an inverter each. The amplifiers operate out of phase with respect to each other and are coupled together by a 0.1µf capacitor. A third inverter serves as a buffer-amplifier for the signal before it enters flip-flop F14, which produces the actual 7 MHz CLK frequency. Initially, the signal is sinusoidal in form, however F14 tends to square up the waveform so it is more acceptable to digital circuits.

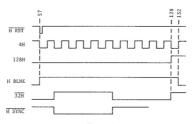

# MAIN TIMING/SYNCHRONIZATION

The main timing and synchronization circuitry in this game is a bit different from the way timing and sync are ordinarily accomplished. Normally, 7493 ripple-through counters are used and are arranged in such a way that they count to a certain number and are then reset back to zero before repeating the count. The following circuitry, however, utilizes 74161 (9316) synchronously-presettable four-bit binary counters to generate the main timing signals. This type of counter is used extensively in motion circuits because it is capable of being preset to any desired number but is used in this circuit because it is a rising-edge triggered device. By keeping all devices rising edge triggered, many problems are avoided. Because of these counters, the following sync circuitry may be a bit confusing at first, but if you regard it as a motion chain which is preset to a base number before counting, it should be easier to com-

The functions of this circuit are primarily twofold: (1) Main timing generates submultiples of CLOCK which are used in most circuits of the game to provide precisely timed signals used in the development of other, more complex, signals where all signals have a synchronous relationship to CLOCK and to the movements of the electron beam. (2) Some of these submultiples are combined to form sync signals which synchronize the operations of the vertical and horizontal oscillators in the TV monitor with the operation of the PCB computer.

HORIZONTAL MAIN TIMING: The horizontal main timing counter chain divides the frequency of CLOCK 29 or 512 times to produce various submultiples of CLOCK known as 1H, 2H, 4H... 256H. The first two counters provide eight bits and flip-flop M10 supplies the ninth. When examined with the video probe, the submultiples appear as a series of vertical columns where the width double with each successive division.

The horizontal reset pulse  $(\overline{\rm H~RST})$  is produced at AND gate P11 and, although it has been named  $\overline{H}$  RST, it is actually a load pulse rather than a reset. If 7493s were used in this circuit, the name  $\overline{H}$  RST would be appropriate for the signal would in fact reset the counters back to zero. However, in this circuit the H RST pulse loads the base number into the 74161s, so it would have been more appropriate to have named this signal

In any case, H RST is generated by the addition of the terminal counts (TCs) from the two counters and from flip-flop M10. Since the terminal count of the first counter is 15, the TC of the second is 240 and the output of M10 256, the resulting reset (read load) pulse occurs at a count of 511 (15 + 240 + 256 = 511).

This is where things may begin to get a bit confusing. The number 511 is actually not the number used to determine line length, although the last point of the line occurs at 511. Since a base or preset number of |1|0|0|1|1|1|0|0| is loaded into the parallel entry terminals of the counters, the horizontal chain always begins counting from this number and the actual line length is 511 minus 57 or 454 clock pulses long. In other words, the H RST pulse occurs on the 454th clock pulse and this point coincides exactly with the time when the electron beam reaches the end of the line at the right side of the CRT.

The result of all this is that each line of the raster has been divided into 454 separate time elements where each element corresponds to a separately addressable point which may be illuminated to form an image. This being true, one can say that 1H equals two clock pulses and that points along the line are spaced 1H apart beginning with 57H and ending

The timing relationships used in the development of both H BLNK and  $\overline{H}$  SYNC are illustrated in Figure 12. First,  $\overline{H}$  RST clears flip-flop Fl4 and then 128H goes HI at 128. However, the count of 128 is actually equivalent to 71 since H RST occurs at 57 (128 - 57 = 71). This HI is clocked through 4 clock pulses later by 4H or on the 75th clock pulse, producing an H BLNK window 75 clock pulses wide which extends from 57 to 132. Any output of F14 is limited to the period of time this window is HI.

HORIZONTAL SYNC: H SYNC is developed at NAND gate H14 and it is interesting to note that two of the signals used in the development of the sync pulse are entirely unnecessary.

In any case,  $\overline{32H}$  at H14-13 is LO until the 64th clock pulse, at which time it rises HI and remains HI until the 96th clock pulse. The result is an H SYNC pulse which is LO between 64H and 96H. Notice that both 64H and 256H are connected to H14 and that both signals are entirely extraneous to the operation of the circuit. They were probably included to avoid a recurring sync pulse, but this extra protection is not necessary since the pulse is limited to the blanking window. Both the inputs can be eliminated with no adverse effect on the circuit.

Figure 12 Development of H SYNC

VERTICAL MAIN TIMING: The Vertical Main Timing circuit is virtually identical to the horizontal one except that it counts H RST pulses rather than clock pulses. Since each H RST pulse coincides with the termination of a line, the vertical timing circuit counts lines per field whereas the hoirzontal counts points per line. The vertical reset pulse coincides with the termination of one full field of horizontal lines.

Two counters and a flip-flop provide none divisions of  $\overline{H}$  RST where each successive division is one-half the frequency of the previous one. The nine resulting outputs are called 1V, 2V, 4V...256V. The vertical reset pulse is developed by ANDing the TCs of the counters (15V + 240V) with the output of the ninth-bit flip-flop (256V). The result would be a pulse at 511 except that, since these counters are preset with the base number |1|1|1|0|1|1| (239), the vertical reset pulse actually occurs with the 272nd H RST pulse (511 - 239 = 272). Therefore, there are 272 horizontal lines per field where each line has a separate address number.

VERTICAL BLANKING: Since V BLNK is the output of the ninth bit of the chain, it is actually equal to 256V. At the time of "reset" (actually load), V BLNK is LO and stays LO until the second counter fills up again. This produces a V BLNK pulse 17V wide which occurs between 239V and 256V.

Figure 13 Development of V SYNC

# VIDEO SUMMATION

However incongruous it may seem to explain the operation of the Video Summation circuitry before the signal inputs themselves are developed and explained, the fact nevertheless remains that Video Summation is organized with sync on the schematic and therefore must be explained here.

Although the primary function of any video summing circuit it to add all the separate video signals across the appropriate values of resistors and couple them to the monitor, this circuit performs a certain amount of signal development and sync protection as well.

The various displays involved in the summation process are the score, the race cars, the control car(s), the grass, the hay bales and both the stripes. All the video information generated separately for each player (e.g. R CARS, STRIPE) is entered at multiplexer R13 for separation by 128V. The score information (SCR VID) and the control cars (C CAR) are summed later in the circuit and do not require multiplexing as they are separated in the circuits which generate these signals.

Multiplexer R13 is a Quad 2-to-1, however only 3/4 are needed here. Since the device is selected by 128V SW, the information in the one player mode will fill the screen, but each player's information will be separated at 128V when in the two player mode.

FLASH: The FLASH signal is generated by NANDing each player's crash signal (CRSH I or CRSH 2) with signal D4 at gate F13. Signal D4 is the very slowly pulsing output of a counter in Section 7. If a crash has occurred, CRSH 1 or CRSH 2 will be HI, enabling this pulsing signal through F13, causing the appropriate player's side to flash.

STRIPE, GRASS & HAY BALES: The grass (those two light areas between the stripe and the edge of the CRT) is developed at B10. Signal 2V is exclusively ORed with 128V at FI1 which, when gated with STRIPE, at F13, reduces the width of the stripe to a narrow line at the top of the CRT and two narrow lines at the bottom. It may be difficult for you to see the very bottom line, depending on how the vertical height of your monitor is adjusted. This signal is then used to clock B10. Since V BLNK clears B10, B10-6 is HI when the flip-flop is cleared at the very beginning of the raster. Therefore, the grass is enabled from the top of the CRT until the first stripe occurs which disables F13 and toggles B10 and turns off GRASS. GRASS then remains LO all the way down the CRT until the next stripe again toggles the flip-flop. This again enables GRASS and the electron beam is intensified until it encounters the very bottom Stripe which again disables GRASS. GRASS remains disabled until V BLNK clears B10 at the top of the CRT.

Notice that the signal GRASS from B10-6 is NANDed with the output of E12-12. There is a very specific reason for this, H BLNK and V BLNK are first ORed together, then inverted before being gated with GRASS. Therefore, the signal resulting from D12-11 will be disabled during both vertical and horizontal blanking which is necessary to prevent GRASS from disrupting sync. The signal from E12-12 simply "locks out" GRASS during horizontal and vertical sync to prevent tearing and other undesir-

After the grass is fully developed and locked out during sync, the resulting signal is gated with the hay bales (RUNR 1 and RUNR 2) at B13 which passes the grass signal, but limits the hay bales to the height of the grass window. Inversion is performed at A15 to make the image white before entering the multiplexer.

As mentioned before, the width of the stripe window is reduced by the signal at F11-6 before it is chopped up by SR116 and R216 at E14 and H13. SR116 and R216 are vertical columns which serrate the stripe window so it appears as a dotted line and the result is inverted before multiplexing so it appears white. Since SR116 and R216 are motion outputs from the Course Speed circuit, the dotted line moves at the course vel-

The rest of the video is entered at F12 and notice that this gate is equipped with a strobe input connected to E12-12 to lock the signal out during sync. NOTE: ONLY TEXAS INSTRUMENT'S 7425 HAS THE STROBE INPUT BONDED TO THE CHIP. SO IF THE ORIGINAL CHIP FAILS AND IT IS REPLACED WITH A 7425 MANUFACTURED BY ANOTHER COMPANY, THE SIGNAL WILL NOT BE LOCK-ED OUT DURING SYNC AND THE RESULTING VIDEO WILL BE COMPLETELY DISTORTED.

- 8. LP: HI, LO & PULSING.

- SC: Pulses HI & LO for .1397µs. 9. LP: HI & PULSING. SC: Pulses LO for .1397us every

- 63.434us. 10. LP: HI & PULSING.

- SC: Pulses LO every 17.2ms for 63.434115

- 11. LP: LO & PULSING. SC: Pulses LO every 17.2ms for 253.7µs.

- 13. LP: HI & PULSING.

- SC: TP12 serrated by TP11.

- 14. LP: HI, LO & PULSING.

- VP: Light area outside borders. 15. LP: HI & PULSING.

- VP: Light horizontal stripe de-

- 16. LP: HI, LO & PULSING.

- VP: Light and dark columns moving with top hay bales.

- 17. LP: HI, LO & PULSING.

- VP: Light and dark columns moving with bottom hay bales.

- 18. LP: HI & PULSING. VP: Fully developed upper stripe

- moving at course velocity. 19. LP: HI & PULSING. VP: Fully developed lower stripe

- moving at course velocity. 20. LP: LO going HI when C CAR #2

- crashes. 21. LP: LO going HI when C CAR #1

- crashes.

- 22. LP: Slowly pulsing signal.

- 23. LP: HI & PULSING. VP: Top hay bale signal inverted 26, LP: HI & PULSING. and extending down the CRT.

- 24. LP: HI & PULSING. VP: Same as above TP except for bottom hay bales. 25. LP: HI, LO & PULSING.

- SC: Pulses HI every 63.434µs for

- 10.4µs & every 17.2µs for 1.08ms.

- VP: GRASS darkens.

- SC: Pulses HI every 63.434µs for 10.4us when GRASS is LO.

- 27. LP: HI when in 1 player mode; HI: LO & PULSING when 2 player. VP: No visible signal during one

- player mode; CRT divided in half 30. LP: HI & PULSING. during 2 player mode.

- 28. LP: LO & PULSING. VP: Top & bottom stripes visible.

- 29. LP: HI going to HI, LO & PULSING when CAR #1 crashes in 1 player mode; pulses faster when either car crashes in 2 player mode.

- VP: Lightens hav bales. 31. LP: LO & PULSING.

- VP: Lightens R CAR images. 32: LP: LO & PULSING.

- VP: Lightens C CAR image(s). 33. LP: LO & PULSING.

- VP: Lightens score images.

- 34 I.P. HT & PHISTNG

- VP: Darkens GRASS images. 35. LP: HI & PHISING. VP: Darkens STRIPEs, C CARs, R CARs and SCORE.

- 36. LP: HI, LO & PULSING. VP: Light column extending from left edge of CRT to 16H to right

- of score numbers. 37. LP: HI during game over and 2

- player; LO during 1 player. 38. LP: Same as TP36 during 2 player operation; LO for 1 player. VP: Same as TP36 during 2 player operation; LO for 1 player.

Figure 14 Main Timing/Sync/Video Summation Schematic

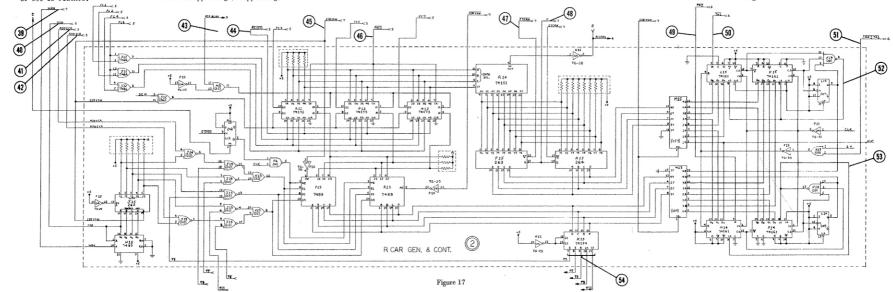

# R CAR GENERATION & CONTROL

INTRODUCTION: The computer-controlled or race car (R CAR) images are both developed and controlled in this section. The degree of complexity found in this circuit is much greater than in most motion circuits because not only are there two normal motion circuits, but the section also contains complex window control circuits as well as an unusual "scratch pad" memory. This complexity combined with the fact that the schematic is drawn with signal processing logically proceeding from right to left and from bottom to top may tend to make this circuit a bit difficult to grasp at first.

To make comprehension easier, the entire circuit may be subdivided into smaller, more easily manageable, sub-sections. Two standard horizontal motion circuits are located at the extreme right of the section and these consist of the familiar nine-bit presettable counter chains plus two separation multiplexers. The outputs of the first chain address ROMS 263 and 264 to retrieve information used in the generation of the car images. The remainder of the circuitry to the left of the ROMs develops signals which select and strobe multiplexer R14 and this circuitry is also divisible into two sections. Counter H15 addresses ROM J15 which reads out a stored code used to randomize windows generated at K15. These windows are temporarily stored in RAMs Pl3 and Rl3 which in turn control latches R12, P12 and M12. The latch outputs then select R14 and form the complete car images.

THE MOTION CIRCUITS: When the machine is conditioned to the two player mode, these circuits control the horizontal motion of both sets of race cars which are separated by a line passing across the CRT at 128V. When in the one player mode, only one set of cars is enabled which fill the In the one player mode, only one set of cars is enabled which fill the entire screen. We will assume the machine is set to the two player mode for much of the following R CAR discussion. The horizontal motion circuits follow the standard configuration used in every video game, however we will explain motion circuit operation in detail. Vertical race car motion is controlled by the Arithmetic Logic Unit (ALU) found in the Processor, but vertical motion is displayed in this circuit.

The illusion of motion is achieved by rapidly shifting the car image in much the same way the illusion of motion is created on the motion picture screen by the film in the projector. The eye perceives the positional shift as motion because of a phenomenon known as "retinal after-image". This phenomenon causes the last seen image to be "remembered" for a very short period of time and, as the position of the image is shifted a number of times in rapid succession, the eye overlaps the images and the brain interprets the shifting process as continuous motion. This process is enhanced by the persistence of the phosphor coating on the inside of the CRT which causes the image to linger, even after the electron beam is moved or shut off.

The speed or velocity of the image is controlled by the shift rate/frame rate ratio. In other words, if the position of the image is shifted

once every frame, it will appear to move much faster than if it were shifted only once every three frames.

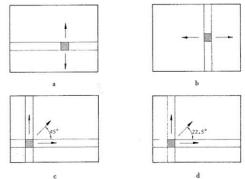

7

The direction of the moving image is controlled by varying the rate at which the vertical and horizontal motion windows are shifted with respect to each other. As the window in Figure a moves up and down, the image contained within it also moves up and down. Figure b shows the horizontal motion window which controls the left-right motion of the image. When the two windows are combined, the image at the intersection can be vectored at any desired angle by individually varying the rate at which each window is shifted. For example, if the two windows are shifted equally, the resultant vector will be 45° (Figure c). But if the horizontal window is shifted twice as fast as the vertical, the image will move along a 22.5° vector (Figure d).

The motion circuits are constructed almost identically to the sync circuits and they run in parallel with their horizontal sync counterpart. If the operation of the motion circuits is timed with that of horizontal sync, the image will be generated in the same place each frame and will appear to be stationary. However, if the motion circuits develop their signals a little sooner or later than sync, the window will be shifted an amount equal to the resulting differential and will appear to move.

The differential is produced by loading different codes at the parallel inputs of the motion counters which controls the point at which these counters begin. The stop code is that number which times the motion circuits with the sync chain and causes a cessation of motion. Other codes, both higher and lower, cause a change in this relationship and the position of the image is shifted with respect to sync.

HORIZONTAL MOTION: Since horizontal reset is always loaded with the number 57, the code entered at the parallel entry terminals of the motion counters which stops motion is also 57. Notice that all the inputs to these counters are tied either HI or LO with the exceptions of the two least significant bits (LSBs). Since the signal at the A input of LIS and M14  $(\overline{\text{TAI}} \text{ or } \overline{\text{TA2}})$  is normally HI, the resulting code at the inputs is |1||0||1|1|1|0|0 or 57.  $\overline{\text{TAI}}$  and  $\overline{\text{TA2}}$  are produced in Section 6 of the schematic and can be seen with the video probe at the very bottom of the CRT. These signals are developed using Analog Timing and accelerator inputs so the motion count may be controlled via the accelerator and its adjustment pot. Both signals are LO only when active and then for a period of time which causes an increase or decrease in the shift rate/frame rate ratio.

The B input or second LSB of the first counter is controlled by  $\overline{\text{CAR TRG}}$  ORed with 2V and inverted by F15 and this output is normally LO and PULSING.  $\overline{\text{CAR TRG}}$  is produced by clocking stored information from ROM 269. When viewed with the video probe at H13-1, it appears as a 2V wide horizontal line at the very top of the CRT. When ORed with 2V, the result is a one line wide signal. Since this is entered at the  $2^1$  bit of the counter chain, the number 59 will be loaded once per field.

Varying the two LSBs produces the three motion codes this circuit uses: 56, 57 and 59. Since the number 59 is always loaded once per field, the motion chain is advanced two clock pulses with respect to sync and the images will be shifted two clock pulses per field. The result is that the car image appears to be overtaking the more or less stationary control car (C CAR). This is true only so long as  $\overline{\text{TAI}}$  or  $\overline{\text{TA2}}$  is HI and the number 56 is not being loaded at the bottom of the CRT.

As the accelerator is depressed,  $\overline{\text{TAI}}$  or  $\overline{\text{TA2}}$  goes LO for one clock pulse. If the accelerator is held down, the pulse width of  $\overline{\text{TAI}}$  or  $\overline{\text{TA2}}$  increases so that it is loaded more times per field. If under the least acceleration,  $\overline{\text{TAI}}$  or  $\overline{\text{TAI}}$  are LO for only one clock pulse per field which produces a code of 58 at the motion chain inputs. This still advances the motion counters with respect to sync and the race cars appear to be losing ground to the control car. The more the acceleration increases, the more times 56 is loaded and retards the motion chain a greater amount causing the control car to appear to be overtaking the race cars at an ever increasing rate of speed.

The outputs of both counter chains enter the inputs of multiplexers MI5 and MI3, but notice that the four LSBs of the top chain enter MI3. Both are Quad 2-to-1 multiplexers which are selected by 128V SW. When the game is in the one player mode, 128V SW remains HI which selects only the first player's race cars. When in the two player mode, 128V SW acts like 128V and separates the CRT into upper and lower halves. The first player's race cars appear in the lower half and the second player's in the upper half.

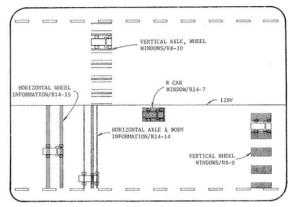

THEROMS: After multiplexing, the four LSBs from the first chain are used to address ROMs 263 and 264. These are 8-bit by 32-word ROMs (see page 2) and two are necessary since the largest size race car is 16 bits long which requires the addition of two eight bit words. Notice that the outputs of both ROMs are OR-tied and since this type of ROM has open collector outputs, they can be operated in this fashion without the outputs of one trying to pull the outputs of the other. These ROMs are addressed by a five bit word where the first four bits are the four LSBs from the

counter chain and the fifth is controlled by signal C. Notice also, that both ROMs are enabled at pin 15 by 2 SCRN or 2 SCRN which produces two differently sized sets of cars. When the machine is in the one player mode, 2 SCRN and  $\overline{2}$  SCRN are LO and HI respectively which selects RI5 and the larger sized race cars result. Since more images need to be squeezed into the CRT when in the two player mode, 2 SCRN goes HI and  $\overline{2}$  SCRN drops LO which selects PI5 and the smaller sized images appear.

If you examine the inputs to the ROMs with the video probe, you can view the address patterns which bear no particular meaning other than this is the way the information is organized within the ROM. However, if you examine the ROM outputs, you can see the horizontal car image information being read out of the ROM (Figure 15). For example, pin 4 of P15 reveals the horizontal information used to generate the wheels, P15-7 produces information for the axles and body and P15-9 creates the center of the car body. RIS stores very similar information except for the larger sized cars.

Figure 15 R Car Generation Data

This information enters multiplexer R14 where it is selected by vertically moving windows to produce the complete car image, but more about this later

HORIZONTAL WINDOWS: This section consists of decoder K13, counter H15, ROM J15, NOR J14 and OR H13. Decoder K13 is a 4-to-16 addressed by the four MSBs from the bottom counter chain. The result is a series of 52H wide windows moving according to the motion chain differential. These horizontal windows are divided at 128V and are areas which limit the image horizontally. The windows are combined with the outputs from ROM 262.

RCM 262 is addressed by counter HIS which simply counts from 0 to 15 extremely slowly. HIS is clocked by WRN which is signal V RST divided 32 times or, in other words, a pulse occurring every 32 fields. If you happen to own a logic clip, this is an excellent place to use it because the counter is operating so slowly that it can actually be observed. At any rate, the outputs sequentially address the ROM which then reads out a simple stored code. This code provides the psuedorandom signal which causes the windows from KI3 to move in an unpredictable fashion.

THE MEMORY CIRCUIT: After combination with the ROM outputs, the windows are temporarily stored in RAMS P13 and R13. The RAMS provide a "scratch pad" memory for the psuedorandom motion. Note that there are two memories and that P13 is selected by T28V SW. If the machine is set to the two player mode, P13 operates the top cars and R13 serves the bottom ones.

There are 16 different locations for storing four-bit words in the RAM, although only three are used here. The data is written during the one clock pulse wide WE (Write Emable) pulse which occurs coincidently with the first clock pulse of the line. The data is read out for the rest of the line by the count from the four MSBs of the motion chain. The result is 16 three-bit words which are used to control the information coming from the 74173 latches.

The latches are equipped with tri-state outputs (low impedance HI and LO states, but high impedance off state) which permits OR-tying of the outputs. Inputs M and N are control lines for turning the outputs on or

off and these inputs are active LO. G1 and G2 are data enables and the data is loaded when these controls are both LO.

The vertical motion signals FL1, FL2, FL4 and FL8 are produced by the Processor and are moving horizontal bars which are ORed with each other. This information is loaded into the appropriate latch by FC3, FC5 or FC7 in conjunction with the output from JL2-8. FC3, FC5 and FC7 are also produced by the Processor. The vertical motion information is then read out by the output of M9-11 in conjunction with the outputs from the RAMs. The output of M9-11 is developed by RCR BIMK. You can see with the video probe that RCR BLNK is the horizontal component of the score window and it keeps the race cars from appearing in the score area. Since this signal is LO all the way across the CRT except in the score area, the Minputs of the latches are enabled for most of the line and the outputs will be enabled as soon as the N inputs forp LO.

If you examine the data inputs to R14 with the video probe, you will notice the ROM information entering. For example, the horizontal wheel information for the small car appears at pin 2. At pins 9, 10 and 11 however, you will see vertically moving windows which select only certain parts of the ROM information so that it is limited in the vertical dimension as well. Since this signal is moving vertically, the vertical motion of the resulting image is controlled. The strobe input at pin 7 of R14 contains complete rectangular windows for the car images. These windows are 16 lines high by 32 clock pulses long for both sizes of cars.

#### TROUBLESHOOTING THE RAMS

Random Access Memories are used both in this circuit and in the Processor. These RAMs could conceivably be tested by entering a known word, controlling the address location of that word and checking the output word with a logic probe while manipulating the ME and WE pins the whole time. But since this requires controlling ten pins while reading four others, it would seem that this technique is unnecessarily difficult. Since there are a number of RAMs in this game and since the correct operation of these devices is both critically important and difficult to check, we are recommending the following troubleshooting procedure.

This technique involves comparing the suspected RAM on the PCB with a known-to-be-good reference RAM. It does not require removal of the suspected RAM, however a simple comparator circuit will have to be built.

Building the comparator requires an IC clip, three IC sockets (2-14 pin and 1-16 pin), a reference RAM (7489), a package of exclusive ORs (7486), a hex inverter (7404), four resistors (2200) and four LEDs. Wire the IC clip pins to the other pins indicated in Figure 16 in such a way that, when the clip is placed on the suspected RAM, the pins of that RAM will be connected to the comparator as indicated. Use #22 AWG stranded wire to connect the IC clip and #30 AWG wire for the rest of the circuit.

Since the outputs from both the reference and the suspected IC are all connected in matched pairs to the exclusive OR gates, the output of the OR will go HI if the inputs do not match. This HI is inverted by one of the inverters (which also act as buffers) and the resulting LO sinks enough current through the LED to light it. Therefore, any incorrect test RAM outputs will be immediately indicated by a lighted LED.

Figure 16 The RAM Comparator Circuit

- 39. LP: Very slowly pulsing signal. 43: LP: HI, LO & PULSING.

- 40. LP: Pulses at half of TP59 rate. 41. LP: LO going HI when a score of

- 400 is reached.

42: Same as TP41, except when score of 200 is reached.

- 43: LP: HI, LO & PULSING.

VP: Light column extending from left edge CRT to right of score.

- 44. LP: HI & PULSING. VP: Vertically moving horizontal bars disappearing & reappearing.

- 46. LP: LO & PULSING. SC: See timing diagram PHI 2.

- 47. Same as TP37. 48. LP: HI, LO & PULSING. VP: Looks like 1H.

45. Same as TP27.

- 49. LP: HI & PULSING. VP: Narrow dark bar at bottom of CRT. Becomes wider and narrower depending on setting of SET TOP SPEED and ACCEL pots.

- 50. Same as TP49.

- 51. LP: HI & PULSING.

- 52. LP: HI & PULSING. VP: Dark vertical line moving with 1st player's R CARs.

- 53. LP: HI & PULSING.

VP: Dark vertical line moving

- with 2nd player's R CARS.

54. LP: HI & PULSING.

VP: Dark horizontal windows moving with R CARS.

## SCORE & TIME DISPLAY

Looking at the score display on the CRT, it is easy to assume this is just another seven-segment display. That is, until the numeral "l" comes up. The shape of this numeral should immediately indicate that this is not a normal score display and, when the schematic is examined, you will in fact see that two ROMS (267 and 268) are used in this circuit. Whereas a seven-segment display creates different numerals by turning the a, b, c, d, e, f and g segments on and off through a BCD to seven-segment decoder, this circuit simply stores and recalls entire numerals. Additionally, this circuit does not count the score, it merely displays it. The score storage functions are performed by the Processor which outputs HL score signals to the display circuit. The whole numerals stored by the ROMs and individually selected at multiplexer RS by the HL signals are strobed by a window signal which causes them to appear in the proper places on the CRT.

Since there are two OR-tied ROMs, they must be selectively enabled and this is done by entering HL8 and  $\overline{\rm HL8}$  at the appropriate inputs. Since a single ROM would not hold enough information, two are used where each stores a few numbers. The actual numbers are read out by 2H, 4H, 8H, 2V and 4V at the address inputs. The complete numerals are always being read out by the resulting address code. For example, if you examine R8-13 with the video probe, you will see the CRT filled with 1s and 9s. The numeral 1 is stored by one ROM and the 9 by the other and since the ROMs are OR-tied, both are displayed simultaneously. To display only one numeral, we must disable the other ROM.

All of the numerals appear at the inputs of R8 and the individual ones needed are selected by the conditions of the signals at the A, B and C inputs. For example, to select the numeral 4, the top ROM is enabled and the code  $1\ 1\ 0$  is entered at the A, B and C select lines of R8.

Three different sets of numbers may be displayed on the CRT depending on whether the machine is in the one or two player mode. In the two player mode, the time information is displayed in the center of the score window and consists of two numerals which count down from 99. Each player's score appears in his side of the score window and is displayed by three digits which count up from 0 0 0. If in the one player mode, only the time and first player's information appear.

Figure 18 Numeral Generation

The horizontal dimension of the score window (RCR BLNK) is developed by Cll and its P8 gate. The vertical windows change according to how many players are in the game and if a game is in progress or not. This information is developed by the remaining P9 gates and both the horizontal and vertical windows are then gated together to form completely bounded areas for the numerals.

The development of the horizontal score window is a bit unusual. Remember that H BLNK goes LO at horizontal reset and stays LO for 75 clock pulses and it clears C11 when it drops LO. After 75 clock pulses, it returns HI and this HI is clocked through on the falling edge since C11 is a master-slave flip-flop. At this time 16H is LO, but at 14H 16H rises HI and stays HI until 160H at which time it again returns LO and toggles the flip-flop. Therefore, RCR BLNK occurs between 57 and 160 or for a total of 103 clock pulses. Although the right hand boundry of this window occurs at the correct place, the whole window is too large, so RCR BLNK is gated with 16H at P8 and the result is a 16H wide horizontal score window which occurs within the RCR BLNK window. The horizontal score window is then divided up vertically into individual score windows for the time and players by the signal from P8-6.

The conditions of the vertical inputs determine whether the score for one or two players is displayed. If in the one player mode, 2 SCRN is LO and this signal disables V CHAR 2 (Vertical Characters-2nd player) and

a HI is produced from P8-3. This HI enables  $\overline{V}$  CHAR  $\overline{I}$  through P8-11 and, if examined with a video probe, this signal appears as two vertical windows which provide areas for the first player's score and time information. However, if the game is in the two player mode, 2 SCRN is HI which allows  $\overline{V}$  CHAR  $\overline{I}$  and provides the upper window as well. Since these windows are much too large for the numerals, the vertical window information at P8-11 is gated with  $\overline{SV}$  and the result at P8-6 is windows which are properly spaced apart from each other vertically and turned on for the correct players

Figure 19 Score & Time Display Windows

9

Notice that the B select (pin 10) of R8 is controlled by the output of C12-8. This signal is used to prevent the time display from counting when the game is not being played. G.O. (Game Over) is the end game signal and it is HI during the attract mode (before the game is started) and LO during the play mode. This signal controls DT (Display Time) which is the vertical window for the time numerals. During the game, G.O. is LO and DT is HI only during the time display window. Therefore, the output at D12-6 is LO only during the time display window and then only while a game is in progress. Only during this time can the information at HL2 read out numerals other than zero for the time display.

Since the outputs from P8-8 and P8-6 are normally HI. M9 acts essentially like an AND gate waiting for two LOs before M9-8 will go LO which activates the active LO strobe input of R8. Therefore, R8 is enabled only during the horizontal score window produced from P8-8 and during the vertical window from P8-6.

# ADD CARS/EXTENDED PLAY

This circuit adds more race cars to the field as scoring increases to increase the degree of difficulty. It also generates the extended play signals XPI and XP2 which enter the Game Control circuit and extend the game length as an award for achieving high score. The point at which the extended play is awarded is user-programmable by changing the positions of the switches located at PCB position J10.  $\overline{D7}$  and  $\overline{D8}$  are also produced in this section and are used by Game Control to end the game.

The ROM stores a simple code, wherein the specific word is selected by the code at the HL score inputs from the Processor. In other words, the ROM output is determined by the player's score. ODD is simply V RST divided 64 times, or a very slowly pulsing line (approximately once per

The first, second and either the third, fourth, fifth or sixth bits of the ROM (depending on which switch is closed) are entered at the inputs of the latches. Each player has a separate latch where J11 is used for the first player and Kll for the second. The latches are alternately selected by 128V SW which divides the screen during the two player mode. The latches are clocked by MSD1 or MSD2 so the latches are enabled only when the most significant digit of the score is being displayed.

Let us assume we have closed the first score adjustment switch. In the truth table, this corresponds to connecting the line underneath "2". Therefore, when the score accumulates to 300, extended play will go into effect when the connected line goes LO. Cars are added when the information from the ROM goes HI. For example, ADD 1 CAR occurs when a score of 400 is reached and ADD 2 CAR at 200.

|                |                                                                                              | 024                                     |                        |

|----------------|----------------------------------------------------------------------------------------------|-----------------------------------------|------------------------|

|                |                                                                                              | 01234567 日刊出                            |                        |

| 0=000<br>0=000 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14                 | 00 00 00 01 1 10 00 00 0 00 00 00 00 00 | ADD 1 CAR<br>ADD 2 CAR |

| 000=1          | 16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31 | 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 |                        |

Table 1 Truth Table For Add Cars/ Extended Play

#### BORDERS

This section consists of two sub-circuits which generate signals needed by the Processor.

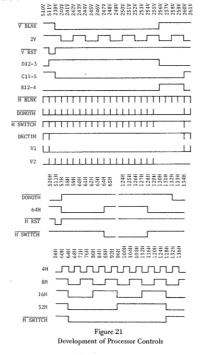

The upper circuit uses sync outputs to develop DONOTH which is used in the Processor to halt Processor functions and to generate H SWITCH. H SWITCH is then used to develop V1 and V2. See Figure 21 for the following discussion.

V BLNK clears Cl1 at 239V causing the Q output of this flip-flop to drop LO. 2V after V BLNK returns HI, or at 260V, Cl1-5 also returns HI producing a pulse which is HI from 239V to 260V. Meanwhile, V RST is NANDed with V BLNK at D12. Since V RST is LO for one clock pulse between 511V and 239V and V BLNK is LO from 239V to 256V, the inverse addition of these signals produces a HI pulse extending from 511V to 256V from D12-3. This signal and the signal from C11-5 are NORed at B12 to produce a signal which is HI from 256V to 260V. This signal is in turn NORed with H BLNK at B12 and the output at B12-4 disables the H BLNK pulses occurring in the interval between 256V and 260V. Since the H BLNK pulse extends from 57H to 132H, each DONOTH pulse is HI during this period.

H SWITCH is developed by NANDing DONOTH, H RST and 64H at P11 in the Processor. DONOTH forms a HI window from 57H to 132H, part of which is selected by 64H. Since 64H is HI between 64H and 128H, H SWITCH is also HI during this time. H RST is an extraneous signal.

To develop V1, H SWITCH is ANDed with the signal from C11-5 which disables the H SWITCH pulses from 239V to 260V. V2 is formed by a similar process, except that the signal from D12-3 enables H SWITCH pulses from 239V to 256V

The bottom circuit develops BDRY II and BDRY using BDRY I. LDVL and 2V. BDRY I is read out from a ROM in Section 6 and it appears simply as a horizontal white bar across the middle of the CRT. NANDing this with 2V reduces the window in width and inverts it so it appears black. The resulting signal  $(\overline{BDRY\ II})$  is gated with LDVL (Leading Vertical Divider Line) from the Game Control circuit and again inverted so it appears white. This white line is then ORed with GRASS at M9 and the resulting signal (BDRY) is HI from the top of the CRT down to and including the bottom of the stripe window.

## COURSE SPEED

The race course consists of moving dotted white lines (stripes) and sets of bars (hay bales) moving along with the dotted lines. While this circuit does not actually generate these displays (this is done in Video Summation), it does develop signals which cause the final displays to move horizontally and in proportion to acceleration. SR116 and R216 both serrate the stripes and cause them to move while RUNR 1 and RUNR 2 perform a similar function with the hay bales.

The function of a moving race track is to impart the feeling of motion to a more or less stationary control car. As the control car picks up speed, velocity is indicated by causing the track to move past the car, as if the car were actually passing a dotted road line and objects along the track. Even though the control car is not really moving, the player interprets the relative speed between his control car and the moving track and is "tricked" into thinking his car is actually moving.

The basic construction and operation of these motion circuits are identical to the circuits used in the generation of R CARs. Therefore, we will not dwell on the basic concepts of motion circuits and their operation and will refer you instead to pages 7 to 9 for a comprehensive analysis of the subject.

A few specifics do bear mentioning here, however. Notice that, like R CAR, these circuits utilize the analog inputs  $\overline{TA1}$  and  $\overline{TA2}$  to control acceleration and that both of these signals are connected to the LSB-input of the first counter. However, the course motion circuits, unlike R CAR, have their second LSBs tied LO permanently and there is a very good reason for this. If the second LSBs could go HI, the number 59 would be loaded once per field and the course would appear to be overtaking the control cars at quite a good clip. Since hay bales and dotted lines do not normally move about, it would be quite strange to be passed on the track by a hay bale!

The operation of both TA signals here is similar to that of R CAR. If either TAI or TAZ are HI, the number 57 is loaded into the appropriate chain which stops motion. But if either signal is LO, 56 is loaded causing the count of the appropriate chain to become retarded by one clock pulse. As acceleration increases, the width of TAI or TA2 increases and it is loaded more times per field, increasing motion to the right. As the track display moves to the right, the control car image appears to be travelling to the left.

The 32nd count of the chain (QA output of C15 or C14) is called SR116 or R216. When viewed with the video probe, these signals appear as 32H wide vertically moving columns where the accelerator and the speed adjustment pot control the velocity. These signals are then taken to the Video Summation circuit where they are used to serrate the windows for both stripes which turns the solid stripes into moving dotted lines.

The preliminary signal for forming the hay bales is produced at D14 where the  $\mathrm{Q}_A$ ,  $\mathrm{Q}_B$  and  $\mathrm{Q}_C$  outputs of the second counters are NORed to produce a non-recurring hay bale window of the desired width. Signal 2S is the result of exclusively ORing 128V with 2V and it is used to separate the hay bale window into a stack of bars. Since the hay bale windows are generated simultaneously with the stripe serration signals, they move together at the same rate.

- 55. Inverse of TP37.

- 56. LP: HI, LO & PULSING.

- VP: Dark bars from 368V to 399V and from 432V to 479V.

- 57. LP: HI, LO & PULSING. VP: Light bars from 288V to 335V. 368V to 399V & 432V to 479V.

- 58. Same as TP43.

- 59. LP: HI & PULSING.

- VP: Dark windows over numbers. 60. LP: HI & PULSING.

- VP: Dark bar over hundreds digit in 1st player's score.

- 61. LP: HI & PULSING.

- VP: Dark bar over hundreds digit in 2nd player's score.

- 62. Same as TP41.

- 63. Same as TP42.

- 64. LP: LO & PULSING.

- SC: See timing diagram for V1.

- 65. LP: LO & PULSING. SC: See timing diagram for V2.

- 66. LP: LO & PULSING. SC: See diagram for DONOTH.

- 67. LP: LO & PULSING.

- VP: Narrow light bar in center of CRT during 2 player mode; 1/4 down CRT during I player mode.

- 68. LP: HI & PULSING. VP: Dark bars in same locations as TP68 except only 2 lines wide.

- 69. LP: Pulses LO for =32.5ms, 32.5 ms after coin switch is closed.

- 70. LP: HI. LO & PULSING. VP: Inverse of TP60 with GRASS

- added. Hi when TP69 drops LO. 71. Same as TP50.

- 72. Same as TP49.

- 73. LP: LO & PULSING.

- VP: Dark vertical line moving

- with 1st player's hay bales. 74. LP: LO & PULSING. with 2nd player's hay bales.

- VP: Dark vertical line moving

- 75. Same as TP17.

- 76. Same as TP16.

- 77. Same as TP23. 78. Same as TP24.

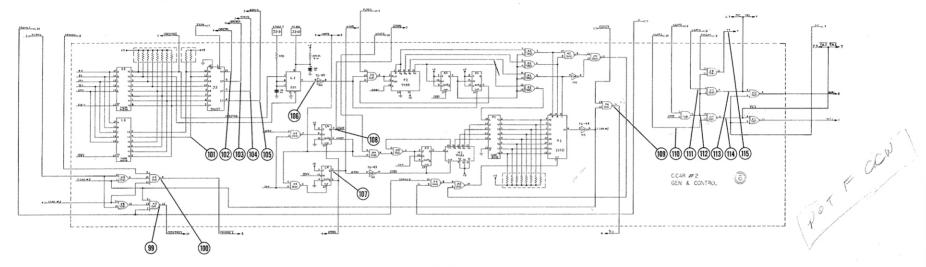

# C CAR #1 GENERATION & CONTROL

The generation and control of the first player's car is identical to the generation of the second player's car (see C CAR #2, Section 6, page 11) with one minor exception. Since this circuit is used both in the single and in the two player modes, it must be capable of generating two differently sized car images, hence the inclusion of another ROM. The ROMs are selected at pin 15 by 2 SCRN or  $2\,$  SCRN depending on whether the game is in the one or two player configuration. For example, when the game is in the two player mode, J1-15  $(2\,$  SCRN) is HI, K1-15  $(2\,$  SCRN) is LO and the larger size car image is selected.

Also, notice that the second player's control car (C2) is gated with the first player's at M4 and the result is inverted by M5 before going to Video Summation for display.

- 79. LP: HI & PULSING.

- VP: Dark narrow horizontal bar 1.5 inches from bottom of CRT. 80. LP: HI & PULSING.

- VP: Dark narrow horizontal bar in center of CRT.

- 81. VP: Light area extending from center of CRT to a position determined by the setting of the steering pot. Cannot extend beyond the line defined by TP79.

- VP: Variable width dark vertical column changing with settings of Accelerator and C CAR position (H RAMP) pots.

- 83. LP: HI, LO & PULSING.

VP: Light vertical column ext-

- ending from 256H to 416H. 84. LP: HI & PULSING.

- VP: Dark vertical column extending from 256H to 288H.

- 85. LP: HI during 1 player mode; HI § PULSING during 2 player mode. VP: Inverted image of C CAR #2 in 2 player mode.

- 86. LP: LO & PULSING. VP: Light horizontal bar passing through the center of C CAR #1.

- 87. LP: HI. LO & PULSING. VP: 1H except where light bar in TP86 passed through car.

- in TP86 passed through car. 88. LP: LO & PULSING.

- VP: Intensifies C CAR images.

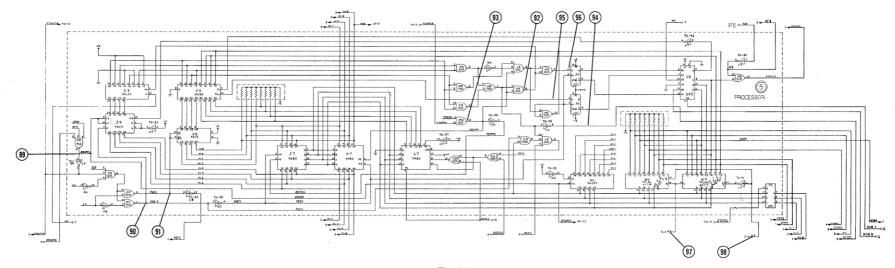

# THE PROCESSOR

The Processor is the most complex circuit in this game, if not in any video game ever produced. Even though this circuit may not appear especially large, the signal flow is difficult to follow, there are many events occurring with extremely complex timing relationships and the entire architecture of the circuit is new to video games. The circuit is essentially a "hard-wired" microprocessor, and so those of you who have had microprocessor experience will find this circuit easier to understand, at least from a conceptual point of view.

Basically, the Processor is little more than an elaborate counter which can be controlled to perform a number of functions at different times on various types of information. Three types of information are handled by the Processor and a different time or mode has been allotted to each. During these modes, the Processor recalls the "old" information from memory, "updates" it and returns it back to the same location in the memory. The three groups of information are (1) the score and time data, (2) the horizontal R CAR information and (3) the data used to control the vertical movements of the R CARs.

But before we delve into the actual operation of this complex circuit, we must first build a solid foundation by describing certain important signal inputs, their timing relationships and various terms and definitions associated with the Processor.

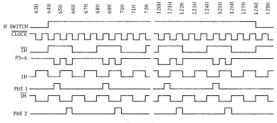

THE PROCESSOR CLOCK: In the analysis of the Borders circuit (Section 3), we discussed the development of a number of signals such as H SWITCH, DONOTH, V1 and V2. The operation of these signals is extremely important to the Processor as are the signals PHI 1 and PHI 2, the Processor system clocks. Two phases of the Processor clock are generated so that the RAMs can be loaded at different times with respect to each other and so that data can be loaded into the latches at a different time than the data is loaded into the RAMs. The development of both phases of the clock is illustrated in Figure 20. Both signals occur only during the period when H SWITCH is active (between 64H and 128H) and each, active H SWITCH period contains 16 PHI 1 and PHI 2 pulses which are out of phase by one clock pulse with respect to each other.

The development of these signals begins when H SWITCH at P3-3 goes HI at 64H and drops LO at 128H providing a 54H wide window at P3 in which PHI I and PHI 2 may be developed. Since  $\overline{\text{CLK}}$  is connected to P3 instead of CLK, the count advances on the falling edge and this is an important factor to keep in mind. Also connected to this gate is the signal 2H and the result is two one-clock-pulse-wide signals which can occur only within the 2H window. This output is connected to one of the inputs of the two M7 NORs and lH or  $\overline{\text{IH}}$  is connected to the other input. Therefore, there must be two LOs at these NORs before the output can go HI. For example, when  $\overline{\text{IH}}$  is LO and the signal from  $\overline{\text{P3}}$ -G is also LO, a one clock pulse wide

PHI 1 pulse occurs. Even though our timing diagram shows only a few examples, be aware that there are 16 PHI 1 and PHI 2 pulses per each active H SWITCH period. This is a particularly important point because the memories are organized as 16 words of four bits each, hence all locations are addressed during each H SWITCH period.

Figure 20

Development of the Processor Clock

THE INSTRUCTION CYCLE: A complete instruction cycle consists of the process by which the data to be updated is recalled from memory, entered in the ALU, has the necessary operation performed on it and is finally returned back into the same location in the memory. Notice that the input latch K9 is clocked by PHI 1 and the output latch J8 is clocked by PHI 2. Therefore, each instruction cycle can be said to extend from the rising edge of PHI 1 to the falling edge of PHI 2.

THE ALU: The 74181 Arithmetic logic Unit is capable of performing as many as 32 different operations on two four-bit words entered at the A and B inputs. The specific function is selected by the address code at the four function select lines  $(S_9-S_3)$  in conjunction with the state of the carry-input (Cn) line. The output code appears at  $F_0-F_3$ . Since two of the function selects are tied together, only four of the 16 normal operations are enabled, however this number is exapndable to eight, depending on the state of the carry-input.

| ALU | SELE | CTS | Cn=0    | $C_{n}=1$ |

|-----|------|-----|---------|-----------|

| 0   | 0.0  | 0   | F=A+1   | F=A       |

| 0   | 1 1  | 0   | F=A-B   | F=A-B-1   |

| 1   | 0 0  | 1   | F=A+B+1 | F=A+B     |

| 1   | 1 1  | 1 1 | F=A     | F≃A-1     |

Table 2 ALU Functions

Whenever the carry-input is HI, the ALU subtracts the number one from the operation is would have performed had the carry-in been LO. For example, when the code at the selects is 0 1 1 0, the ALU subtracts B from A if the carry-in is LO. However, if the carry-in is HI, the ALU subtracts 1 from (A-B).

PROCESSOR MODES: The four Processor modes are controlled by the code developed by mode controls V1 and V2.

Table 3 Processor Mode Controls

In Mode 1, the Processor is idle and this inactive period is used to read out miscellaneous information from the program ROMs needed in other circuits. The vertical windows for the score and time displays ( $\overline{V}$  GHAR 1,  $\overline{V}$  CHAR 2 and DT) are stored in these ROMs as are signals MSD 1, MSD 2 and MSDT (the Most Significant Digit for the first and second players and for the time).

In Mode 2, the vertical R CAR position information stored in K7 is updated by reading it out of memory, performing the necessary operation on it (e.g. adding one) and re-loading it back into the same memory location. Mode 3 provides a period in which the score and time information stored in J7 can be updated as necessary. Similarly, Mode 4 is used to update the horizontal R CAR position or velocity and this information is stored in PAM #7

GENERAL PROCESSOR ARCHITECTURE: The addressing of the entire four-bit system is provided by multiplexer K6 which outputs either a fast or slow address code. This system address controls both ROMs, all three RAMs and decoder R6. Although the ROMs do produce certain miscellaneous signals used in other circuits, their primary function is to provide the system program. In other words, the ROMs tell the Processor which function to perform next. The ROMs select L6 which controls the carry-input of the ALU and they also select the ALU function at ALU inputs  $S_0/S_3$  and  $S_1/S_2$ . The random logic to the left of L6 is used in conjunction with the ROMs to test for a 10 or 15 condition at the ALU outputs so that proper decimal and binary counting can be achieved. K9 and J8 are input and output latches provided for the ALU which – as mentioned before – provides the actual arithmetic operations. The information processed in this circuit is stored in RAMs J7, K7 and L7 and a different RAM is used for each separate group of information.

SPECIFIC COMPONENT FUNCTIONS: Now that we have developed the input signals to the Processor and described the general architecture of the circuit, we can turn out attention to the specific operation of the components before discussing individual mode operation.

MULTIPLEXER K6: This multiplexer develops the system address which has both a fast and a slow version. When H SWITCH is active, a fast code (4H, 8H, 16H and 32H) addresses the circuit for the first 64 clock pulses of each line. Thereafter, the slow address (16V, 32V, 64V and 128V) is used. This has been done specifically so the information can be written into the RAMs quickly, at the beginning of the line, then read out more slowly, 16 lines at a time.